# Energy-Aware Mobile Processor Architectures: A Systematic Review of Design Principles and Optimization Methods

Vivek Sharma

System Analyst

MITS Deemed University

Viveks@Mitsgwalior.In

**Abstract**—The increasing need for high-performance and high-energy efficiency in mobile computing has resulted in significant innovations in mobile processor architectures. This review article examines some of the major design concepts and algorithm optimization techniques that can be used to ensure energy efficiency and computational power balance in mobile devices. It explores such architectural innovations as RISC-V, logic-memory co-integration, and system-level technologies as clock gating, power gating, and dynamic voltage and frequency scaling (DVFS). Moreover, the paper also discusses software-hardware co-design options, thermal-aware scheduling, and the new machine learning-based energy prediction and management approaches. This study gives us an idea of the dynamic nature of mobile processor design to enhance performance with longer battery life through synthesis of the existing research and developments. The findings are especially applicable because mobile applications are becoming increasingly more demanding with regard to computation. The mentioned techniques can be considered the basis of future innovation in the cellular energy optimization and chip architecture.

**Keywords**—Mobile Processor, Energy-Efficient Computing, System-on-Chip (SoC), Dynamic Voltage and Frequency Scaling (DVFS), Power Gating, Clock Gating, RISC-V.

## I. INTRODUCTION

The integration of memory and logic in the same silicon substrate has been the long-term problem of complementary metal-oxide semiconductor (CMOS) technology. There have been historical trends in terms of technological advancement of logic chips and memory. However, convergence has been driven in a massive way since the inception of embedded memories, and it is understandable: embedded memories enhance the performance of a system and reduce power consumption. Power-delay product is a relevant indicator of power efficiency, and it simply renders it improved. This energy-optimal connection of logic and memory integration is intrinsic and provides a principle on energy-aware architecture design.

Mobile sensing applications in domains as diverse as medicine, transportation, and social media have been on the rise because of the diffusion of high-tech smartphones with embedded sensors and enhanced processing and communication capabilities [1]. It is predicted that even more sophisticated sensors incorporated into future smartphones and allow them to support highly personalized and context-aware user applications [2]. The most important aspect of these mobile sensing systems is that it must have client-side middleware capable of connecting to the internal sensors and sending data to external storage devices, to enable the analysis of an individual or a group of data.

The engagement time of users has grown significantly as the smartphones continue to develop and gain popularity [3]. In order to be competitive smart phone makers have invested in improving performance, adding battery life, and improving user experience. The high frequency multi-core processors have been adopted as a result of these demands. The

consumption of power has however gone up, though, as a result of the improved processing capacity. To address this trade-off, manufacturers employed the strategy that includes adding capacity to the battery and low-power technology though those approaches only yield some small improvements.

A battery-powered phone is one of the nature of the constraints of a smart phone. A faulty battery is capable of not allowing the user to carry out the most important functions and therefore, energy efficiency is a serious non-functional criterion in the design of mobile applications. Mobile software energy efficiency has been an environmental issue of concern, as the total energy consumption of the billions of smartphones worldwide has raised the association of green software engineering and sustainability. These have emerged as burning interdisciplinary issues especially in the area of software engineering. Although studies have shown that developers are becoming more conscious of energy related issues [4], two major challenges are encountered by the developers namely a lack of proper knowledge and the lack of good tools to create energy efficient mobile systems.

### A. Structure of the Paper

The following is the outline of the paper: Section II deals with systems on a chip (SoC) architectural design and energy saving techniques. Section III explains the battery limitations and power management using design concepts. Section IV discusses the computing requirements in today's applications in energy optimization methods. Section V provide related literature and Section VI a conclusion with key insights and future directions.

## II. FUNDAMENTALS OF MOBILE PROCESSOR ARCHITECTURES

Communication and embedded applications are the two main drivers of the rapid proliferation of microprocessors, and embedded processors have become part of the numerous gadgets in the home, such as televisions, audio systems, kitchen appliances, and automobiles high-end vehicles such as BMWs now contain 60 to 70 microprocessors that control braking, airbag systems, window operation, and more. On average there are almost 60 embedded microprocessors in mobile devices and appliances in an average American family. This development is based on the design of mobile processors (and in particular System-on-Chip (SoC) designs) whereby size, power, and performance are optimized through the integration of many components into a single chip. These components are CPUs, GPUs, memory, modems and power controllers. These architectures are developed based on market-specific needs and end-product limitations focusing on a trade-off between high performance, low power consumption, low cost, and small form factors. Some of the preferences exhibited by manufacturers in the design are also whether to use thin modem or fat modem, RF integration strategies, and the consolidation of components at the system level [5]. They are low-end mobile products with greater integration since that costs less, though with reduced processing power. The architecture of mobile processors has over the years developed the task-specific and simple designs to elegant, power-efficient and AI-accelerated SoCs. Trends show that in the future, there is still a concern on improving AI processing, energy performance, real-time responsiveness, and smooth connectivity in progressively smaller silicon footprints.

### A. Key Components of Mobile Processor Architecture

Recent mobile SoCs are designed to include multiple heterogeneous processing units that are specific to computational tasks:

- **Central Processing Unit (CPU):** The general-purpose core which controls and performs sequential tasks is called the CPU. Mobile CPUs are usually configured to be performance and power efficiency balanced, and usually use ARM architecture, including Cortex-A and Cortex-M series with big. LITTLE or DynamIQ configurations.

- **Graphics Processing Unit (GPU):** The GPU executes workloads that are planned, i.e. parallel, e.g. 3D rendering, image processing and more recently machine learning inference. Mobile GPUs such as Mali created by ARM and Adreno created by Qualcomm are designed to be high performance on a per-watt basis.

- **Digital Signal Processor (DSP):** DSPs are used to perform real-time functions such as audio filtering and voice recognition consuming low power and being highly efficient. DSPs were originally independent ICs, but now are found integrated into SoCs and are common in VLSI designs [6]. Mobile handsets are dominated by programmable DSPs as they are flexible. The DSPs became a necessity with the introduction of the digital mobile signal processing (2G (GSM) systems, as opposed to the analog 1G systems.

- **Neural Processing Unit (NPU):** NPUs are specific hardware accelerators of deep learning inference which have much better performance and energy

efficiency on AI workloads like facial recognition and natural language processing. AI-capable SoCs are also coming to use NPUs.

- **Memory Hierarchy:** Designing memory hierarchy is an essential aspect in mobile SoCs, which typically contains multi-level caches (L1, L2, and occasionally L3), on-chip SRAM and external LPDDR memory [7]. Memory access and bandwidth optimization are critical towards keeping the latency and energy consumption at a minimum.

The interactions between them dictate the total computational throughput and power consumption of the SoC and hence the co-design and schedule strategies of SoC-based energy-optimization are considered as the core of energy-aware software development..

### B. Power and Energy Consumption in Mobile Devices

The mobile device market has been showing promising trends, yet, several issues with its implementation still require correction in case the quantity of devices present in the market is to keep increasing [8]. Power, capacity, security, and quality are the primary obstacles. Research into mobile phones in recent years has been substantial, allowing for a comprehensive literature review on mobile energy conservation and consumption as well as studies of various features and components of mobile devices [9]. With the addition of voice calls and text messaging, mobile devices transform into full-fledged multimedia systems over the next decade. This method of assessment relies on Moore's Law. A few examples of the many features that mobile phones offer are built-in GPS devices, video and music players, high-quality cameras, short-range communication technologies, and enormous data levels for Internet connections. These technologies are used to design a number of solutions. All of these apps and services are connecting with each other through the phone's wireless air interface. It is obvious that different mobile phone services use energy. Evidently, all the features that point to wireless air interfaces being power hungry basically mean that the phone's battery life minimized. Because Moore's law predicts that all areas of computing technology eventually experience exponential growth, including batteries, this is a problem that phone manufacturers must solve.

### C. Sources of Energy Inefficiency

The energy inefficiencies prevalent in mobile processor architecture stem from the interplay between hardware, software, and system inefficiencies. Particularly, dynamic power consumption, which is due to the transistors switching frequently and particularly during times of high clock frequency and/or heavier workload is probably one of the major causes of energy wastage [10]. Also, energy losses related to leakage power occur when transistors are not in use since the state is preserved by supplying power to the voltage node, a factor that is particularly cumbersome in the deep submicron technologies. Energy inefficiency may also be made through the mobile instruction scheduling when it results in too much processing or too many more instructions being followed at the cost of a general expansion of power consumption. As the memory access is considered to occupy a major share of the whole energy consumed by the processors, it can also comprise the power consumed together with off-chip memory. Mobile processing cost just goes beyond access to the computing or processing capabilities. Transferring data, such as transfer of data between off-chip

volatile memory and on-chip processor, consumes relatively considerable amount of energy because relatively the cost of data transfer is much high in comparison to the cost of computation. The presence of thermal hotspots and ineffective cooling measures lowered the overall performance of the processors to introduce conservative power management that result in the inefficient energy consumption of mobile processor, in majority of cases. It is important to properly identify and correct these system inefficiencies to come up with energy aware mobile processor architectures.

### III. DESIGN PRINCIPLES FOR ENERGY EFFICIENCY

The challenge of designing mobile processors of low energy consumption needs a multi-faceted approach in which a large variety of hardware and software-based methods are deployed. Dynamic frequency and voltage scaling one of the most fundamental facts that actively reduces dynamic power usage when greater processing power is not needed by adjusting the processor's voltage and frequency in response to workload demands. There are other techniques common, such as the clock gating and power gates technique, which switches off idle circuitry and cuts both dynamic and leakage power at the same time. Architecturally, execution of low-power instructions within an instruction set architecture (ISA) minimizes energy per instruction, establishing performance execution channels as well [11]. Other features besides microarchitectural techniques to conserve energy consist of reducing pipeline depth, having an execution unit with simple instruction set, and better use of caches. The focus in these methods is on the balance amid performance and energy usage as such that mobile processors have sufficient computing capability such that the user can surpass his or her fundamental use-case with promptness whilst maximizing battery life at the macro-scale.

#### A. Dynamic Voltage and Frequency Scaling (DVFS)

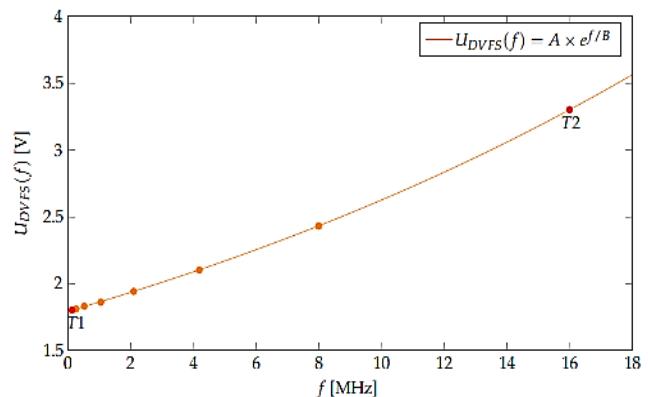

A popular power management strategy, Dynamic Voltage and Frequency Scaling (DVFS) is an expansion of Dynamic Frequency Scaling (DFS) that tries to decrease data centre energy consumption and increase battery life in portable devices. Processor voltage and frequency are dynamically adjusted in response to workload needs, reducing power consumption during low activity and increasing it during high performance to keep the system responsive. This method allows saving a lot of energy without an apparent impact on the performance and is used in the vast majority of modern mobile CPUs. The technologies of Speed Step in Intel, and adaptive DVFS in the Cortex processor using ARM are examples of how this balance is struck in practice [12]. In this regard, it is important to ascertain the right voltage to use in the operation of the microcontrollers or microprocessors since a low voltage may hamper certain functions. To solve this, two reference points were obtained in the microcontroller datasheet which were 0.131 MHz at 1.8 V and 16 MHz at 3.3 V and entered into a microcontroller datasheet in Microsoft Excel 2019 to create an exponential voltage-frequency model via regression analysis. This model aids in effective estimation of the minimum required voltage under several frequencies in order to ensure stable operation as well as maximize its energy efficiency as illustrated in Figure 1.

Fig. 1. Exponential model for stable voltage calculation (red circles mark points T1 and T2)

A non-linear voltage-frequency DVFS model, which emphasizes the non-linear dependence of the voltage required on the frequency in order to maintain constant microcontroller operation. Key points T1 (0.131 MHz, 1.8 V) and T2 (16 MHz, 3.3 V) define the curve, derived through regression analysis. This model aids in efficient voltage scaling for optimized power and performance.

#### B. Clock Gating and Power Gating

Power Gating (PG) and Clock Gating (CG) are complementary rather than exclusive methods of reducing power consumption. Also, CG and PG working together might lessen the space penalty of inserting the control logic of each separate method. Knowledge of the sleep function—the signal that activates and deactivates the sleep transistor—and data on the circuit's clusters groups of gates that controlled by the same transistor form the basis of clustered PG. The clustering process, however, needs to be limited so that CG and PG can share the control logic. To be more precise, pairs of cells controlled by the same register serve as an implicit determinant of the clusters. Of course, there are benefits and drawbacks to this approach. A positive aspect is that it controls the sleep transistors using CG signals. In contrast, the "implicit" clusters' makeup might lead to less-than-ideal cell groupings when it comes to PG application. Prior to deciding to use CG and PG together or separately, it is important to assess the current trade-off between the flexibility in creating PG clusters and the decrease in overhead caused by sharing control logic and signals. Since gate grouping is limited by the current CG structure, the cluster sizes and compositions may no longer be ideal, as previously stated. Size decisions for the sleep transistors are affected by this.

#### C. RISC-VISA

An open instruction set architecture with a comprehensive software toolchain, RISC-V is being used more and more for different types of system on chips. For power-efficient system-on-chips, this advanced RISC instruction set is ideal for use with scalar processor cores [13]. The instructions used by the ISA vary according to their intended use, and its modular nature is evident. Modules of instruction sets that were quite simple were the primary focus of this investigation. The ability to build a basic processor core that can execute the RV32I and RV32IM instruction sets is its strongest suit. The former includes the base integer instruction set while the latter adds integer multiplication and division. The PPAs of every core that was created were measured quantitatively.

#### D. Energy Performance Trade-offs

An essential difficulty in designing energy-aware architectures is establishing a balance between computing performance and energy efficiency. Focusing only on energy optimization could cause unacceptable latency or a diminished user experience, whilst putting performance first can lead to substantial energy overhead. Thus, contemporary systems use adaptive techniques to change their power and performance states (P-states) on the fly according to what the application needs. Designers often rely on performance-per-watt metrics and Pareto optimization to analyze and manage trade-offs. Incorporating machine learning-based prediction models is an emerging approach to optimize energy-performance curves in real-time.

### IV. SYSTEM-LEVEL ENERGY OPTIMIZATION TECHNIQUES

The system level optimizations are required to optimize the overall mobile processor architecture by coordinating the intelligent decisions regarding energy by the software with the hardware capabilities. Processor, memory, OS, and other processor components work together in system-level optimizations, which allow the processor to make global decisions, as opposed to hardware-level optimizations, which focus on individual components. For mobile processors nowadays, the most popular and commonly used feature is dynamic voltage and frequency scaling, or DVFS. Power consumption during idling or low utilization can be greatly reduced with DVFS since the CPU can dynamically adjust the supply voltage and clock frequency depending on the workload. Another optimization that can be used to minimize energy and maximize performance is the scheduling or the way on how to assign the processes to the processor cores. Nevertheless, care should be taken such that the scheduling algorithm looks beyond performance implications and also deals with energy consumption. Managing thermal-related problems improve reliability in the future, particularly as mobile platforms grow to be more performant and thermal management problems become all-important or constitute the bottle neck. Thermal-aware scheduling shifts thermal loading among the cores of processors and reinvents the operation of thermal hotspots, which either decrease the performance or increase the leakage power greatly.

#### A. Energy Management Techniques

Smartphone energy management techniques can broadly be categorized into two areas: practical implementations for energy efficiency and energy assessment approaches [14], as shown in Table I:

TABLE I. CLASSIFICATION OF SMARTPHONE ENERGY MANAGEMENT TECHNIQUES INTO IMPLEMENTATION AND ANALYSIS APPROACHES

| Category        | Description                                                                                                                                          | Examples                                                                                                                                                                                        |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Implementations | Practical methods aimed at reducing energy consumption through software or system-level enhancements.                                                | Development of energy, efficient OS/software-Optimization strategies for existing platforms                                                                                                     |

| Analysis        | Assessment-focused studies that identify high energy-consuming components or evaluate tools and frameworks used in energy measurement and reduction. | Evaluation of energy measurement tools. ENKOC: A mobile network framework for energy-efficient parallel search that reduces localization costs and network traffic using power-law distribution |

Smartphone energy management involves practical implementations to reduce power consumption and analytical approaches to assess and optimize energy use, collectively aiming to improve efficiency and extend battery life.

#### B. Machine Learning-Based Energy Prediction

Numerous studies on ML development have been carried out in the construction industry, with a concentration on energy efficiency, building performance, and occupant comfort. Constructed a machine learning model to forecast energy performance and the energy retrofitting scenario for building components; this was done with an eye towards the energy aspect [15]. Researchers found that ML's great reliability and short processing times made it a potential replacement for traditional technologies used to simulate building performance. One of the four schematic predictive methodologies they used to establish energy projections is an ML method based on long short-term memory (LSTM) that asserts to have a faster computing time than the Energy Plus simulation [16]. In contrast, it developed an ML model using the convolutional neural network (CNN) method to replace a building energy modelling tool. This model successfully predicts thermal energy using a wide range of building designs and climate variables as inputs [17]. ML models that can foretell how well an energy retrofit would work could be a powerful resource for investigating the growing number of options available to inform such decisions [18]. Using a multi-step predictive deep reinforcement learning method based on an LSTM neural network with a generalized cross entropy (GC-LSTM), a newly published study found that smart building HVAC control systems could cut power consumption expenses without sacrificing user comfort. In order to maximize user comfort, the computational framework compares the actual indoor temperature with the predicted outdoor temperature.

#### C. Thermal-Aware Scheduling

Thermal-aware scheduling is a major issue to be taken into account in such energy-alert mobile processor architecture and deals with temperature control and thermal hotspots prevention within processors. Since mobile processors are expected to run in a constrained thermal situation, a lot of heat in the chip can result to throttling, performance loss, higher leakage power, and eventually can be used to compromise the processor hardware, which Thermal-aware schedulers aim at keeping track of thermal profiles of the system and are capable of dynamically scheduling tasks and modifying their execution patterns in such a way that thermal load is balanced across the range of core types and system components [19]. Thermal-aware scheduler have one form of being just prioritizing the low-power tasks, but more advanced thermally-aware scheduler characteristics may alleviate thermal burdens by cold-staging/head-staging or migrating the heat intensive tasks or throttling the overheated core(s) to lower clock frequencies. Finally, proper management of thermal loads through proper consideration of thermal, specific processors can run normal workloads, be efficient, and deliver the performance level which may be limited by a physical environment. Hence, thermal-aware scheduling is state-awareness in the system level energy management pedestrian view.

#### D. Emerging Trends

Modern mobile central processing unit designs aim to improve efficiency and performance by incorporating cutting-

edge technologies. Modern central processing units (CPUs) can now use machine learning models to foretell how workloads behave, which allows them to better manage resources, reduce energy loss while switching between tasks, and handle multitasking with ease [20]. Additionally, the integration of Neural Processing Units (NPUs) supports AI-driven tasks such as voice and facial recognition, with dedicated cores like Apple's Neural Engine and Qualcomm's Hexagon delivering significantly better performance than general-purpose cores. Another notable development is the increasing use of advanced manufacturing nodes, such as 5nm and 3nm technologies. These nodes allow more transistors to be incorporated in a small area, which results in better performance, less power usage, and reduced leakage current. There are leading semiconductor vendors such as TSMC and Samsung who are using these state-of-the-art nodes in high-end mobile CPUs, such as: the A17 Bionic of Apple and the Snapdragon 8 Gen 3 of Qualcomm.

## V. LITERATURE OF REVIEW

This literature Summary examines recent advancements in energy-aware mobile processor architectures, highlighting thermodynamic modeling, ASIP design, femtocell-based frameworks, power delivery networks, robotic system optimization, and architectural energy efficiency, emphasizing performance gains, power reduction, and future research opportunities across domains.

Dou, Liu and Xiao (2025) Introducing MobiRL, a scheduler that uses reinforcement learning to smartly modify the frequency of the CPU and GPU on mobile platforms in order to meet user needs precisely. Autonomous learning to optimize UI smoothness and power consumption, MobiRL monitors the mobile system status and adjusts CPU/GPU frequency. Experiments conducted on recently shipped smartphones demonstrate that MobiRL reduces power consumption by 42.8% and the frame drop rate by 4.1% compared to the popular commercial scheduler. In addition, MobiRL has a lower frame loss rate (up to 2.5%) and lower power usage (32.6%) compared to a study that used Q-Learning for CPU frequency scheduling. Products for mobile phones have included their method [21].

Hübner et al. (2025) explores the architectural aspects and possible performance gains of the Apple Silicon M-Series System on a chip (SoC) for high-performance computing (HPC), including the CPU and GPU designs, the unified memory architecture, and coprocessors like Advanced Matrix Extensions (AMX). It then creates and implements benchmarks in Metal Shading Language and Objective-C++ to evaluate computational and memory performance, while also measuring power consumption and efficiency with Apple's power metrics tool. The results show that the M-Series chips have comparatively high memory bandwidth and substantial improvements in computational performance, especially the GPU surpassing the CPU starting with the M2 and reaching a peak performance of 2.9 FP32 TFLOPS for the M4. All four processors achieve an efficiency of more than 200 GFLOPS per Watt, with power consumption ranging from a few watts to 10–20 watts [22].

Bonen et al. (2025) Architectural principles were established from the bottom up. LNL improved the

performance and efficiency of core partitioning, added fine-grain power delivery, revised idle state management, reduced CPU wakes, improved memory subsystem power states, and optimized clusters with a single threaded core. It could also reduce software load to the desired hardware at runtime. Along with NVMe's premium features, LNL included memory-on-package, a power management integrated circuit, a robust neural processing unit, a memory-side cache, and whole storage encryption. This LNL design able to operate between 8 W and 30 W+ and also with LPDDR5 up to 8533 MHz [23].

Jung et al. (2025) a semantic LiDAR-PNN-SLAM (LP-SLAM) system is described to have a real-time semantic LiDAR SLAM processor (LSPU) which provides real-time 3-D segmentation, localization, and mapping using point neural networks (PNNs). The LSPU implements the LP-SLAM and has the following capabilities: 1) a kNN cluster, with 2-D/3-D spherical coordinate-based bin (SB) searching; 2) a PNN engine (PNNE) with a global point-level task scheduler (GPTS) to maximize core utilization using two-step workload balancing; 3) a key point extraction core (KEC) to skip unnecessary computation in the sorting operation; and 4) an optimization cluster with configuration-capable computation modes to support key point-level pip. The result is that the suggested LSPU uses 99.89% less energy than current CPU + GPU platforms, accomplishes 20.7 ms of processing time, and demonstrates real-time semantic LP-SLAM [24].

Peng et al. (2024) developed a heat transfer model of the processor of a mobile computing device based on thermodynamics. Considering Lindauer's principle, the maximum computing rate of the processor is derived. Moreover, the performance of devices adopting multi-processor is evaluated, where each processor works periodically to complete the computing task. The conditions for stable computing and the thermodynamic advantage of multi-processor are given. Based on the evaluation, an optimization method is proposed to lower the average temperature of the processor, and simulation results show that the maximum computing rate can be improved up to 20.9% [25].

Park et al. (2024) present an advanced application-specific instruction-set processor (ASIP) design for touch controller systems, efficiently accelerating various signal processing algorithms for high-quality touch detection problems on resource-limited mobile devices. Mapping to the baseline ARM Cortex-M3 embedded processor, identify critical bottlenecks in the target touch detection algorithm by measuring the processing time of major functions. An ASIP architecture is newly defined by introducing touch-aware single-instruction multiple-data (SIMD) instructions. Implementation results show that adding the proposed ASIP core to the baseline SoC solution enhances the processing efficiency of critical functions by more than 2 times while increasing the overall area costs by only 8% [26].

A comparative analysis of recent research on energy-aware mobile processor architectures is provided in Table II, with various approaches, main findings, implementation difficulties and future research directions having been outlined to achieve better energy efficiency.

TABLE II. LITERATURE SUMMARY ON ENERGY-AWARE MOBILE PROCESSOR ARCHITECTURES WITH DESIGN PRINCIPLES AND OPTIMIZATION METHODS

| Author               | Study On                                                                       | Approach                                                                                                                             | Key Findings                                                                                                                                                      | Challenges                                                                                                         | Future Directions                                                                                                                    |

|----------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Dou, et al. (2025)   | Intelligent CPU/GPU frequency scheduling on mobile devices                     | Reinforcement Learning-based scheduler (MobiRL) that adjusts CPU/GPU frequencies for optimal performance and energy savings          | 4.1% reduction in frame drops - 42.8% power savings over commercial schedulers. Outperforms Q-learning method by 2.5% in frame drops and 32.6% in power reduction | Generalization across different device architectures; trade-off between learning cost and real-time responsiveness | Extension to heterogeneous architectures and multi-task optimization; integration with other subsystems like NPU and display engines |

| Hübner et al. (2025) | Assessment of Apple Silicon M-series SoCs for High Performance Computing (HPC) | Architectural analysis and performance benchmarking of M1–M4 chips using Metal and Objective-C++                                     | GPU outperforms CPU in M2 onward - Peak 2.9 FP32 TFLOPS (M4), Over 200 GFLOPS/W efficiency for GPUs. Effective memory bandwidth utilization                       | Limited FP64 performance; constrained software ecosystem for HPC                                                   | Enhancement of GPU FP64 capabilities; improved support for open HPC toolchains on Apple platforms                                    |

| Bonen et al. (2025)  | Power-optimized hybrid core architecture (LNL) for mobile processors           | Design of LNL architecture with performance/efficiency core partitioning, fine-grained power delivery, and advanced power management | Reduced CPU wake-ups. Improved power states for memory subsystem. Integrated NPU, memory-side cache, NVMe encryption                                              | Complexity in runtime workload distribution; hardware-software co-optimization needed                              | Scalability toward edge and AIoT devices; tighter integration with AI accelerators                                                   |

| Jung et al. (2025)   | Real-time Semantic SLAM Processing for LiDAR systems                           | Hardware accelerator (LSPU) implementing LP-SLAM using PNN, kNN clustering, and optimized pipelining for 3D perception tasks         | . 20.7 ms real-time semantic SLAM processing and 99.89% energy reduction vs. CPU+GPU setups                                                                       | Hardware complexity; adapting to diverse LiDAR hardware and real-world scenes                                      | Generalization to multimodal SLAM; scalability for autonomous vehicles and robotics applications                                     |

| Peng et al. (2024)   | Heat transfer and thermodynamic modeling of mobile processors                  | Thermodynamic model + performance evaluation of periodic multi-processor systems                                                     | Multi-processor systems reduce average temperature; computing rate improved by 20.9%                                                                              | Maintaining stable computing under thermal constraints                                                             | Optimization methods to enhance thermal efficiency and computing throughput                                                          |

| Park et al. (2024)   | ASIP design for signal processing in touch controller systems                  | ASIP with SIMD for 2D matrix computing on ARM Cortex-M3                                                                              | Processing efficiency >2×; area overhead only 8%                                                                                                                  | Balancing performance gain vs. hardware overhead                                                                   | Further specialization of ASIP for other high-precision mobile applications                                                          |

## VI. CONCLUSION AND FUTURE WORK

This Study examines the complex interplay between mobile processor architecture, energy efficiency and techniques of optimization at system levels. It points out how logic and memory integration, use of design approaches such as DVFS, clock gating, power gating, and use of compact instruction sets such as RISC-V can be used to achieve considerable improvements in energy-performance of mobile devices. The discussion also highlights the issues of thermal hotspots, inefficiencies in accessing the memory and losses in energy through software and hardware issues. More so, the paper highlights the necessity of holistic optimization of the architecture and system-level in order to increase battery life and maintain performance in the contemporary smartphones. On the whole, energy-conscious design is essential to the future generation of mobile processors to meet more and more complicated applications with finite power constraints.

The future research needs to focus on the creation of intelligent and adaptive energy management systems using machine learning to predict workloads and thermal modelling. There should also be a focus on more intelligent, thermally-aware schedulers that are able to migrate tasks in real time and control clock speed to avoid hardware degradation. The extension of open ISAs such as RISC-V can be used to achieve more architectural innovation and energy efficiency across a diverse range of mobile platforms and co-optimization of hardware with software stack will be critical. Finally, advancing low-power SoC simulation environments and providing better tooling support for developers will address current gaps in building truly energy-optimized mobile applications.

## REFERENCES

- [1] H. Galeana-Zapién, C. Torres-Huitzil, and J. Rubio-Loyola, “Mobile phone middleware architecture for energy and context awareness in location-based services,” *Sensors (Switzerland)*, vol. 14, no. 12, pp. 23673–23696, 2014, doi: 10.3390/s141223673.

- [2] V. Panchal, “Energy-Efficient Core Design for Mobile Processors: Balancing Power and Performance,” *Int. Res. J. Eng. Technol.*, vol. 11, no. 12, pp. 191–201, 2024.

- [3] J. Lee, S. Nam, and S. Park, “Energy-Efficient Control of Mobile Processors Based on Long Short-Term Memory,” *IEEE Access*, vol. 7, pp. 80552–80560, 2019, doi: 10.1109/ACCESS.2019.2923334.

- [4] S. Huber, T. Lorey, and M. Felderer, “Techniques for Improving the Energy Efficiency of Mobile Apps: A Taxonomy and Systematic Literature Review,” *Proc. - 2023 49th Euromicro Conf. Softw. Eng. Adv. Appl. SEAA 2023*, pp. 286–292, 2023, doi: 10.1109/SEAA60479.2023.00051.

- [5] V. Panchal, “Thermal and Power Management Challenges in High-Performance Mobile Processors,” vol. 13, no. 11, 2024, doi: 10.15680/IJRSET.2024.1311014.

- [6] M. PratapSingh and M. Kumar Jain, “Evolution of Processor Architecture in Mobile Phones,” *Int. J. Comput. Appl.*, vol. 90, no. 4, pp. 34–39, 2014, doi: 10.5120/15564-4339.

- [7] S. S. S. Neeli, “Data Protection in the Digital Age: SOC Audit Protocols and Encryption in Database Security,” *ESP Int. J. Adv. Comput. Technol.*, vol. 2, no. 03, pp. 167–172, 2024.

- [8] A. F. Ali, N. H. M. Hatta, and K. T. Wei, “Literature review on energy consumption and conservation in mobile device,” *J. Theor. Appl. Inf. Technol.*, vol. 95, no. 9, pp. 1858–1874, 2017.

- [9] S. Gupta and A. Mathur, “Enhanced flooding scheme for AODV routing protocol in mobile ad hoc networks,” in *Proceedings - International Conference on Electronic Systems, Signal Processing, and Computing Technologies, ICESC 2014*, 2014. doi: 10.1109/ICESC.2014.60.

- [10] P. Renna and S. Materi, “A literature review of energy efficiency and sustainability in manufacturing systems,” *Appl. Sci.*, vol. 11, no. 16, 2021, doi: 10.3390/app11167366.

[11] N. Tatang and T. Ray, "Design and Planning of Energy Efficient Building: A Critical Review," *Int. J. Eng. Res. Appl.* [www.ijera.com](http://www.ijera.com), vol. 12, no. 2, pp. 28–31, 2022, doi: 10.9790/9622-1202012831.

[12] J. Zidar, T. Matić, I. Aleksi, and Ž. Hocenski, "Dynamic Voltage and Frequency Scaling as a Method for Reducing Energy Consumption in Ultra-Low-Power Embedded Systems," *Electron.*, 2024, doi: 10.3390/electronics13050826.

[13] J. Kadomoto, H. Irie, and S. Sakai, "Evaluation of Different Microarchitectures for Energy-Efficient RISC-V Cores," in *Proceedings - 2022 IEEE 15th International Symposium on Embedded Multicore/Many-Core Systems-on-Chip, MCSOC 2022*, 2022, pp. 78–84. doi: 10.1109/MCSOC57363.2022.00022.

[14] Y. Mansour, H. Hammad, O. A. Waraga, and M. A. Talib, "Energy Management Systems and Smart Phones: A Systematic Literature Survey," in *2021 International Conference on Communications, Computing, Cybersecurity, and Informatics (CCCI)*, IEEE, Oct. 2021, pp. 1–7. doi: 10.1109/CCCI52664.2021.9583184.

[15] M. Sari *et al.*, "Machine Learning-Based Energy Use Prediction for the Smart Building Energy Management System," *J. Inf. Technol. Constr.*, vol. 28, pp. 622–645, 2023, doi: 10.36680/j.itcon.2023.033.

[16] N. Patel, "Enhanced Network Security: Real-Time Malicious Traffic Detection in SD-WAN Using LSTM-GRU Hybrid Model," in *2024 9th International Conference on Communication and Electronics Systems (ICCES)*, IEEE, Dec. 2024, pp. 826–833. doi: 10.1109/ICCES63552.2024.10860215.

[17] S. Mathur and S. Gupta, "Classification and Detection of Automated Facial Mask to COVID-19 based on Deep CNN Model," in *2023 IEEE 7th Conference on Information and Communication Technology (CICT)*, IEEE, Dec. 2023, pp. 1–6. doi: 10.1109/CICT59886.2023.10455699.

[18] R. Q. Majumder, "Machine Learning for Predictive Analytics: Trends and Future Directions," *Int. J. Innov. Sci. Res. Technol.*, vol. 10, no. 4, pp. 3557–3564, May 2025, doi: 10.38124/ijisrt/25apr1899.

[19] N. Fisher, J. J. Chen, S. Wang, and L. Thiele, "Thermal-aware global real-time scheduling and analysis on multicore systems," *J. Syst. Archit.*, vol. 57, no. 5, pp. 547–560, 2011, doi: 10.1016/j.sysarc.2010.09.010.

[20] M. Halpern, Y. Zhu, and V. J. Reddi, "Mobile CPU's rise to power: Quantifying the impact of generational mobile CPU design trends on performance, energy, and user satisfaction," in *2016 IEEE International Symposium on High Performance Computer Architecture (HPCA)*, IEEE, Mar. 2016, pp. 64–76. doi: 10.1109/HPCA.2016.7446054.

[21] X. Dou, L. Liu, and L. Xiao, "An Intelligent Scheduling Approach on Mobile OS for Optimizing UI Smoothness and Power," *ACM Trans. Archit. Code Optim.*, vol. 22, no. 1, pp. 1–27, Mar. 2025, doi: 10.1145/3674910.

[22] P. Hübner, A. Hu, I. Peng, and S. Markidis, "Apple vs. Oranges: Evaluating the Apple Silicon M-Series SoCs for HPC Performance and Efficiency," Mar. 2025, doi: 10.48550/arXiv.2502.05317.

[23] N. Bonen *et al.*, "Lunar Lake an Intel Mobile Processor: SoC Architecture Overview (2024)," *IEEE Micro*, vol. 45, no. 3, pp. 15–21, May 2025, doi: 10.1109/MM.2025.3558407.

[24] J. Jung *et al.*, "An Energy-Efficient Processor for Real-Time Semantic LiDAR SLAM in Mobile Robots," *IEEE J. Solid-State Circuits*, vol. 60, no. 1, pp. 112–124, Jan. 2025, doi: 10.1109/JSSC.2024.3450314.

[25] X. Peng, L. Yan, Y. Zhong, T. Han, Q. Li, and X. Ge, "Temperature-based evaluation and optimization of multi-processor mobile computing," in *2024 International Wireless Communications and Mobile Computing (IWCMC)*, 2024, pp. 673–678. doi: 10.1109/IWCMC61514.2024.10592341.

[26] E. Park, M. Jin, and Y. Lee, "Cost-Efficient SIMD ASIP Architecture for Mobile Touchscreen Controllers," in *2024 IEEE International Symposium on Circuits and Systems (ISCAS)*, 2024, pp. 1–5. doi: 10.1109/ISCAS58744.2024.10557834.